澜起科技2023年半年度董事会经营评述内容如下:

一、报告期内公司所属行业及主营业务情况说明

(一)所处行业情况 1、行业的发展阶段、基本特点、主要技术门槛 公司是一家集成电路设计企业,集成电路行业作为全球信息产业的基础,是世界电子信息技术创新的基石。集成电路行业派生出诸如PC、互联网、智能手机、云计算、大数据、人工智能等诸多具有划时代意义的创新应用,成为现代日常生活中必不可少的组成部分。移动互联时代后,5G、云计算、AI计算、高性能计算、智能汽车等应用领域的快速发展和技术迭代,正推动集成电路产业进入新的成长周期。 集成电路行业主要包括集成电路设计业、制造业和封装测试业,属于资本与技术密集型行业。 (1)服务器市场行业情况 公司的产品内存接口及模组配套芯片、PCIe Retimer芯片、MXC芯片、津逮CPU以及混合安全内存模组等主要应用于服务器,因此,服务器行业的发展情况与公司业务紧密相关。服务器是数据中心的“心脏”,其本质是一种性能更高的计算机,但相较于普通计算机,服务器具有更高速的CPU计算能力、更强大的外部数据吞吐能力和更好的扩展性,运行更快,负载更高。基于全球数据总量的爆发式增长以及数据向云端迁移的趋势,新的数据中心建设热度不减,同时围绕新增数据的处理和应用,云计算、人工智能、虚拟现实和增强现实等数字经济方兴未艾,服务器作为基础的算力支撑,从长远来看,整体服务器市场将持续保持高景气度。 2023年上半年,受宏观环境影响,服务器及计算机行业需求下滑,行业整体面临去库存的压力。但随着AIGC的快速发展,将有望带动AI服务器的需求增加,从而一定程度上缓解行业去库存的压力。TrendForce集邦咨询预计,2023年AI服务器(包含搭载GPU、FPGA、ASIC等)全球出货量近120万台,年增38.4%,占整体服务器出货量近9%,至2026年将占15%。 (2)内存模组行业情况 内存模组是当前计算机架构的重要组成部分,作为CPU与硬盘的数据中转站,起到临时存储数据的作用,其存储和读取数据的速度相较硬盘更快。按应用领域不同,内存模组可分为:1、服务器内存模组,其主要类型为RDIMM、LRDIMM,相较于其他类型内存模组,服务器内存模组由于服务器数据存储和处理的负载能力不断提升,对内存模组的稳定性、纠错能力以及低功耗均提出了较高要求;2、普通台式机、笔记本内存模组,其主要类型为UDIMM、SODIMM。而平板、手机内存主要使用的LPDDR通过焊接至主板或封装在片上系统上发挥功能。 内存模组行业的发展主要来自于技术的更新迭代和计算机生态系统的推动。内存模组的发展有着清晰的技术升级路径,JEDEC组织定义内存模组的组成构件、性能指标、具体参数等,2021年DDR5第一子代相关产品已开始量产,内存模组正在从DDR4世代开始向DDR5世代切换,同时JEDEC已初步完成DDR5第二子代、第三子代产品标准制定。内存模组与CPU是计算机的两个核心部件,是计算机生态系统的重要组成部分,支持新一代内存模组的CPU上市将推动内存模组的更新换代。支持DDR5的主流桌面级CPU已于2021年正式发布,普通台式机/笔记本电脑DDR5内存模组逐渐上量;支持DDR5的主流服务器CPU于2022年底至2023年初正式发布,DDR5服务器内存模组渗透率将持续提升。 全球DRAM行业市场90%以上的市场份额由三星电子、海力士及美光科技占据,他们也是公司内存接口芯片及内存模组配套芯片主要的下游客户。 (3)内存接口芯片及内存模组配套芯片行业情况 内存接口芯片是服务器内存模组的核心逻辑器件,其主要作用是提升内存数据访问的速度及稳定性,满足服务器CPU对内存模组日益增长的高性能及大容量需求。 从2016年开始,DDR4技术的发展进入了成熟期,成为内存市场的主流技术。为了实现更高的传输速率和支持更大的内存容量,JEDEC组织进一步更新和完善了DDR4内存接口芯片的技术规格,增加了多种功能,用以支持更高速率和更大容量的内存。在DDR4世代,从Gen1.0、Gen1.5、Gen2.0到Gen2plus,每一子代内存接口芯片所支持的最高传输速率在持续上升,DDR4最后一个子代产品Gen2plus支持的最高传输已达3200MT/s。随着JEDEC组织不断完善对DDR5内存接口产品的规格定义,DDR5内存技术正在逐步实现对DDR4内存技术的更新和替代。DDR5第一子代内存接口芯片相比于DDR4最后一个子代的内存接口芯片,采用了更低的工作电压(1.1V),同时在传输有效性和可靠性上又迈进了一步。从JEDEC已经公布的相关信息来看,DDR5内存接口芯片已经规划了三个子代,支持速率分别是4800MT/s、5600MT/s、6400MT/s,预计后续可能还会有1~4个子代,可见通过不断的技术创新,实现更高的传输速率和支持更大的内存容量将是内存接口芯片行业未来发展的趋势和动力。 根据JEDEC组织的定义,在DDR5世代,服务器内存模组上除了需要内存接口芯片之外,同时还需要配置三种配套芯片,包括一颗SPD芯片、一颗PMIC芯片和两颗TS芯片;普通台式机、笔记本电脑的内存模组UDIMM、SODIMM上,需要配置两种配套芯片,包括一颗SPD芯片和一颗PMIC芯片。 目前DDR5内存接口芯片的竞争格局与DDR4世代类似,全球只有三家供应商可提供DDR5第一子代的量产产品,分别是公司、瑞萨电子和Rambus,公司在内存接口芯片的市场份额保持稳定。在配套芯片上,报告期内,SPD和TS主要的两家供应商是公司和瑞萨电子;PMIC的竞争对手更多,竞争态势更复杂。 为了满足不断增长的AI处理对更高带宽、更高容量内存模组需求,JEDEC组织目前正在制定服务器MRDIMM(Multiplexed Rank DIMM)内存模组相关技术标准。MRDIMM内存模组采用了LRDIMM“1+10”的基础架构,与普通LRDIMM相比,MRDIMM内存模组可以同时访问内存模组上的两个阵列,提供双倍带宽,第一代产品最高支持8800MT/s速率,预计在DDR5世代还会有两至三代更高速率的产品。服务器高带宽内存模组需要搭配的内存接口芯片为MRCD芯片和MDB芯片,与普通的RCD芯片、DB芯片相比,设计更为复杂、速率更高。 在桌面端,随着DDR5传输速率持续提升,到DDR5中期,原本不需要信号缓冲的UDIMM、SODIMM(主要用于台式机和笔记本电脑),将需要一颗时钟驱动器(Clock Driver)对内存模组的时钟信号进行缓冲再驱动,从而提高时钟信号的信号完整性和可靠性。目前JEDEC组织正在制定CUDIMM和CSODIMM内存模组相关标准,包括其中的CKD芯片相关标准,将应用于支持6400MT/S及以上速率的台式机和笔记本电脑。 关于MRCD/MDB芯片和CKD芯片,公司正积极参与国际标准制定和产品研发。 (4)时钟芯片行业情况 时钟芯片是为电子系统提供其必要的时钟脉冲的芯片。在数字系统中,时钟脉冲是集成电路运转的节拍器,在电子系统中扮演着“心脏”的重要角色。高频/高性能数字模块的正确运行需要时钟芯片提供精准的时钟脉冲(节拍)来同步运算操作和数据传输交互。时钟脉冲的性能决定了系统是否能运行到目标速度,时钟芯片不达标有可能导致模块或设备无法运作。 因此,时钟芯片提供的输出时钟需要具备极高的可靠性、宽广的输出频率范围、优良的抖动特性以及扩频功能。 目前,时钟芯片种类主要包括时钟发生器、去抖时钟芯片和时钟缓冲芯片等细分产品。时钟发生器是根据参考时钟来合成多个不同频率时钟的芯片,它是时钟芯片的一个重要类别,是数据中心、工业控制、新能源汽车等领域的基础芯片;去抖时钟芯片是为其他芯片提供低抖动低噪声的参考时钟的芯片;时钟缓冲芯片是用于时钟脉冲复制、格式转换、电平转化等功能的芯片。 根据Market Data Forecast的数据,2021年时钟芯片的市场规模合计为18.82亿美元,预计到2027年可达到30.19亿美元。由于时钟芯片在电子系统中广泛且重要的作用,同时其设计难度较大、技术水平要求较高,因此该类产品的主要市场份额长期被少数几家美日厂商占据。 (5)PCIe及PCIe Retimer芯片行业情况 PCIe协议是一种高速串行计算机扩展总线标准,自2003年诞生以来,近几年PCIe互连技术发展迅速,传输速率基本上实现了每3-4年翻倍增长,并保持良好的向后兼容特性。PCIe协议已由PCIe4.0发展为PCIe5.0,传输速率已从16GT/s提升到32GT/s,到PCIe6.0,传输速率将进一步提升到64GT/s。随着PCIe协议传输速率的快速提升,并依托于强大的生态系统,平台厂商、芯片厂商、终端设备厂商和测试设备厂商的深入合作,PCIe已成为主流互连接口,全面覆盖了包括PC机、服务器、存储系统、手持计算等各种计算平台,有效服务云计算、企业级计算、高性能计算、人工智能和物联网等应用场景。 然而,一方面随着应用不断发展推动着PCIe标准迭代更新,速度不断翻倍,另一方面由于服务器的物理尺寸受限于工业标准并没有很大的变化,导致整个链路的插损预算从PCIe3.0时代的22dB增加到了PCIe4.0时代的28dB,并进一步增长到了PCIe5.0时代的36dB。 如何解决PCIe信号链路的插损问题,提高PCIe信号传输距离是业界面临的重要问题。一种思路是选用低损PCB,但价格高昂,仅仅是主板就可能会带来较大的成本增加,而且并不能有效覆盖多连接器应用场景;另一种思路是引入适当的链路扩展器件如Retimer,使用PCIe Retimer芯片,采用模拟信号和数字信号调理技术、重定时技术,来补偿信道损耗并消除各种抖动的影响,从而提升PCIe信号的完整性,增加高速信号的有效传输距离。 因此,PCIe Retimer芯片作为PCIe协议升级迭代背景下新的芯片需求,其主要解决数据中心、服务器通过PCIe协议在数据高速、远距离传输时,信号时序不齐、损耗大、完整性差等问题。相比于市场其他技术解决方案,现阶段Retimer芯片的解决方案在性能、标准化和生态系统支持等方面具有一定的比较优势,未来根据系统配置,Retimer芯片可以灵活地切换PCIe或CXL模式,更受用户青睐。 而随着传输速率从PCIe4.0的16GT/s到PCIe5.0的32GT/S,再次实现翻倍,Retimer芯片技术路径的优势更加明显,Retimer芯片的需求呈“刚性化”趋势。有研究预测,到PCIe5.0时代,PCIe Retimer芯片有望为行业主流解决方案。 (6)AI芯片行业情况 现阶段,按基本功能划分,AI芯片可分为训练芯片和推理芯片;按技术路径划分,AI芯片可分为GPU、FPGA、ASIC芯片。 近年来人工智能的发展呈现出数据体量爆发式增长态势,算法模型的参数量指数级增加,以加速计算为核心的算力中心对AI芯片的需求不断扩大。除了传统的监控和计算机视觉等业务,AI在向量检索、搜索推荐广告上的应用快速发展,在自然语言处理(NLP)上,特别是LLM(large language models)方向,更是于近期达到了里程碑式的进展,以ChatGPT为首的生成类模型已经成为了人工智能的新热点。ChatGPT等AI大模型已经呈现初步的商业规模,技术服务底座加速成型,关注度和行业应用渗透度上呈现很强活力。多模态大模型在模型参数和榜单准确率上持续突破,微软、百度、阿里等企业都在持续增加投入引领行业发展。 以ChatGPT为代表的基于海量多源数据的大模型,对算力的需求非常高,随着AI模型和应用的进一步发展和规模化,算力需求将持续释放,大算力芯片的市场规模持续增长,将快速推动AI芯片的性能升级。 基于AI应用未来巨大的应用潜力,国内外知名科技企业都在持续加大相关领域的投入。根据IDC《全球人工智能支出指南》做出最新预测,全球AI支出(包括以AI为中心的各类系统的软件、硬件与服务支出),在2023年将达到1540亿美元,较2022年同比增长26.9%。同时,IDC预测,到2026年AI相关产业规模支出超过3000亿美元,2022至2026年的复合增长率达到27%。 2023年6月,AMD在其“数据中心与人工智能技术首映会”上预计:到2027年,数据中心AI加速器总潜在市场规模将增长5倍,从今年的300亿美元左右,以超过50%的复合年增长率增长到2027年的1500亿美元以上。 2、公司所处的行业地位分析及其变化情况 (1)内存接口芯片及内存模组配套芯片 公司的内存接口芯片受到了市场及行业的广泛认可,公司凭借具有自主知识产权的高速、低功耗技术,为新一代服务器平台提供完全符合JEDEC标准的高性能内存接口解决方案,是全球可提供从DDR2到DDR5内存全缓冲/半缓冲完整解决方案的主要供应商之一,在该领域拥有重要话语权。 产品标准制定方面,公司是全球微电子行业标准制定机构JEDEC固态技术协会的董事会成员之一,在JEDEC下属的三个委员会及分会中担任主席职位,深度参与JEDEC相关产品的标准制定。其中,公司牵头制定多款DDR5内存接口芯片标准,包括第一子代、第二子代、第三子代内存接口芯片及第一子代高带宽内存接口芯片MDB等,并积极参与DDR5第一子代CKD芯片和DDR5内存模组配套芯片标准制定。 技术实力方面,公司处于国际领先水平。公司发明的DDR4全缓冲“1+9”架构被JEDEC国际标准采纳。该架构在DDR5世代演化为“1+10”框架,继续作为LRDIMM的国际标准,并进一步作为基础架构衍生出MRDIMM国际标准。在DDR5世代,公司在内存接口芯片领域继续全球领跑,进一步巩固了在该领域的优势。2022年5月,公司在业界率先试产DDR5第二子代RCD芯片。2022年9月,公司发布业界首款DDR5第一子代CKD芯片工程样片。2022年12月,公司发布业界首款DDR5第三子代RCD芯片工程样片。 市场份额方面,公司在DDR4世代逐步确立了行业领先优势,是全球可提供DDR4内存接口芯片的三家主要厂商之一,占据全球市场的重要份额。在DDR5世代,公司继续领跑,内存接口芯片的市场份额保持稳定。公司可为DDR5系列内存模组提供完整的内存接口及模组配套芯片解决方案,是目前全球可提供全套解决方案的两家公司之一。 (2)PCIe Retimer芯片 在PCIe4.0时代,公司是全球能够提供PCIe4.0Retimer芯片的三家企业之一;在PCIe5.0时代,2023年1月,公司量产PCIe5.0/CXL2.0Retimer芯片,是全球第二家宣布量产该产品的厂家。作为PCIe相关的底层技术,公司的Serdes IP已实现突破,相关IP已应用到公司PCIe5.0/CXL2.0Retimer芯片上。 (3)MXC芯片 2022年5月,公司发布全球首款CXL内存扩展控制器芯片(MXC)。该MXC芯片专为内存AIC扩展卡、背板及EDSFF内存模组而设计,可大幅扩展内存容量和带宽,满足高性能计算、人工智能等数据密集型应用日益增长的需求。 MXC芯片推出以来,公司迅速和国内外主要的模组厂商,服务器系统厂商和云服务厂商展开合作,积极推进基于MXC芯片的模组项目设计。目前已经有多家客户推出了采用澜起科技MXC芯片的CXL内存模组及板卡,并在相关服务器平台上通过基本功能验证。公司也在进一步与更多合作伙伴一起探索CXL内存扩展和池化在实际业务场景中的应用和落地,保持在这一市场中的领先优势。 (4)津逮服务器平台 津逮服务器平台是公司面向中国市场设计的本土服务器平台解决方案,其技术具有独创性、先进性,且该产品线可持续更新迭代。鉴于服务器CPU以及内存模组的市场准入门槛较高,需要较长的测试及认证周期,公司作为行业生态的新进入者,需要一定时间在该领域立足。 经过多年的市场拓展,津逮服务器平台已具备一定的客户基础及市场份额,持续的更新迭代提高了津逮CPU的产品竞争力,坚持不懈的客户导入和及时的本地服务也逐步获得客户与市场的认可。2023年2月,搭载澜起津逮CPU的一款服务器产品成功通过专家组检测评审,入选“首批可信计算认证产品”,获颁“可信计算产品认证证书”。公司自2019年推出津逮CPU以来,一直致力于满足本土市场对安全可信计算的需求,不断推进产品更新迭代。相较于市场上其他服务器CPU品牌,津逮CPU不仅在性能和生态兼容性方面比肩国际主流品牌,而且可提供经权威机构认证的硬件信任根,保障计算过程和计算资源不被破坏和篡改,守卫云环境下的数据中心硬件安全。 (二)报告期内公司所从事的主要业务 公司是一家国际领先的数据处理及互连芯片设计公司,致力于为云计算和人工智能领域提供高性能、低功耗的芯片解决方案,目前公司拥有两大产品线,互连类芯片产品线和津逮服务器平台产品线。其中,互连类芯片产品主要包括内存接口芯片、内存模组配套芯片、PCIe Retimer芯片、MXC芯片、CKD芯片等,津逮服务器平台产品包括津逮CPU和混合安全内存模组(HSDIMM)。同时,公司正在研发基于“近内存计算架构”的AI芯片。 互连类芯片产品线 1、内存接口芯片 内存接口芯片是服务器内存模组(又称“内存条”)的核心逻辑器件,作为服务器CPU存取内存数据的必由通路,其主要作用是提升内存数据访问的速度及稳定性,满足服务器CPU对内存模组日益增长的高性能及大容量需求。内存接口芯片需与内存厂商生产的各种内存颗粒和内存模组进行配套,并通过服务器CPU、内存和OEM厂商针对其功能和性能(如稳定性、运行速度和功耗等)的全方位严格认证,才能进入大规模商用阶段。因此,研发此类产品不仅要攻克内存接口的核心技术难关,还要跨越服务器生态系统的高准入门槛。 现阶段,DDR4及DDR5内存接口芯片按功能可分为两类:一是寄存缓冲器(RCD),用来缓冲来自内存控制器的地址、命令、时钟、控制信号;二是数据缓冲器(DB),用来缓冲来自内存控制器或内存颗粒的数据信号。RCD与DB组成套片,可实现对地址、命令、时钟、控制信号和数据信号的全缓冲。仅采用了RCD芯片对地址、命令、时钟、控制信号进行缓冲的内存模组通常称为RDIMM(寄存双列直插内存模组),而采用了RCD和DB套片对地址、命令、时钟、控制信号及数据信号进行缓冲的内存模组称为LRDIMM(减载双列直插内存模组)。 公司凭借具有自主知识产权的高速、低功耗技术,长期致力于为新一代服务器平台提供符合JEDEC标准的高性能内存接口解决方案。随着JEDEC标准和内存技术的发展演变,公司先后推出了DDR2-DDR5系列内存接口芯片,可应用于各种缓冲式内存模组,包括RDIMM及LRDIMM等,满足高性能服务器对高速、大容量的内存系统的需求。目前,公司的DDR4及DDR5内存接口芯片已成功进入国际主流内存、服务器和云计算领域,并占据全球市场的重要份额。 DDR4世代的内存接口芯片产品目前仍是市场的主流产品,报告期内以DDR4Gen2Plus子代为主。 DDR5是JEDEC标准定义的第5代双倍速率同步动态随机存取存储器标准。与DDR4相比,DDR5采用了更低的工作电压(1.1V),同时在传输有效性和可靠性上又迈进了一步,其支持的最高速率可超过6400MT/S,是DDR4最高速率的2倍以上。 (1)DDR5第一子代RCD芯片支持双通道内存架构,命令、地址、时钟和控制信号1:2缓冲,并提供奇偶校验功能。该芯片符合JEDEC标准,支持DDR5-4800速率,采用1.1V工作电压,更为节能。该款芯片除了可作为中央缓冲器单独用于RDIMM之外,还可以与DDR5DB芯片组成套片,用于LRDIMM,以提供更高容量、更低功耗的内存解决方案。 (2)DDR5第一子代DB芯片是一款8位双向数据缓冲芯片,该芯片与DDR5RCD芯片一 起组成套片,用于DDR5LRDIMM。该芯片符合JEDEC标准,支持DDR5-4800速率,采用1.1V工作电压。在DDR5LRDIMM应用中,一颗DDR5RCD芯片需搭配十颗DDR5DB芯片,即每个子通道配置五颗DB芯片,以支持片上数据校正,并可将数据预取提升至最高16位,从而为高端多核服务器提供更大容量、更高带宽和更强性能的内存解决方案。 (3)2022年5月,公司在业界率先试产DDR5第二子代RCD芯片。DDR5第二子代RCD芯片支持双通道内存架构,命令、地址、时钟和控制信号1:2缓冲,并提供奇偶校验功能。该芯片符合JEDEC标准,支持DDR5-5600速率,采用1.1V工作电压,更为节能。 (4)2022年12月,公司在业界率先推出DDR5第三子代RCD芯片工程样片。DDR5第三子代RCD芯片支持的数据速率高达6400MT/s,与第二子代相比,最高支持速率提升14.3%,与第一子代相比,提升33.3%。 2、DDR5内存模组配套芯片 根据JEDEC标准,DDR5内存模组上除了内存颗粒及内存接口芯片外,还需要三种配套芯片,分别是串行检测集线器(SPD)、温度传感器(TS)以及电源管理芯片(PMIC)。 (1)串行检测集线器(SPD) 公司与合作伙伴共同研发了DDR5第一子代串行检测集线器(SPD),芯片内部集成了8KbitEEPROM、I2C/I3C总线集线器(Hub)和温度传感器(TS),适用于DDR5系列内存模组(如LRDIMM、RDIMM、UDIMM、SODIMM等),应用范围包括服务器、台式机及笔记本内存模组。SPD是DDR5内存模组不可或缺的组件,也是内存管理系统的关键组成部分,其包含如下几项功能: 第一,其内置的SPD EEPROM是一个非易失性存储器,用于存储内存模组的相关信息以及模组上内存颗粒和相关器件的所有配置参数。根据JEDEC的内存规范,每个内存模组都需配置一个SPD器件,并按照JEDEC规范的数据结构编写SPD EEPROM的内容。主板BIOS在开机后会读取SPD内存储的信息,并根据读取到的信息来配置内存控制器和内存模组。DDR5SPD数据可通过I2C/I3C总线访问,并可按存储区块(block)进行写保护,以满足DDR5内存模组的高速率和安全要求。 第二,该芯片还可以作为I2C/I3C总线集线器,一端连接系统主控设备(如CPU或基板管理控制器(BMC),另一端连接内存模组上的本地组件,包括RCD、PMIC和TS,是系统主控设备与内存模组上组件之间的通信中心。在DDR5规范中,一个I2C/I3C总线上最多可连接8个集线器(8个内存模组),每个集线器和该集线器管理下的每个内存模组上的本地组件都被指定了一个特定的地址代码,支持唯一地址固定寻址。 第三,该芯片还内置了温度传感器(TS),可连续监测SPD所在位置的温度。主控设备可通过I2C/I3C总线从SPD中的相关寄存器读取传感器检测到的温度,以便于进行内存模组的温度管理,提高系统工作的稳定性。 (2)温度传感器(TS) 公司与合作伙伴共同研发了DDR5第一子代高精度温度传感器(TS)芯片,该芯片符合JEDEC规范,支持I2C和I3C串行总线,适用于DDR5服务器RDIMM和LRDIMM内存模组。TS作为SPD芯片的从设备,可以工作在时钟频率分别高达1MHz I2C和12.5MHz I3C总线上;CPU可经由SPD芯片与之进行通讯,从而实现对内存模组的温度管理。TS是DDR5服务器内存模组上重要组件,目前主流的DDR5服务器内存模组配置2颗TS。 (3)电源管理芯片(PMIC) 公司与合作伙伴共同研发了符合JEDEC规范的DDR5第一子代低/高电流电源管理芯片(PMIC)。该芯片包含4个直流-直流降压转换器,两个线性稳压器(LDO,分别为1.8V和1.0V),并能支持I2C和I3C串行总线,适用于DDR5服务器RDIMM和LRDIMM内存模组。PMIC的作用主要是为内存模组上的其他芯片(如DRAM、RCD、DB、SPD和TS等)提供电源支持。CPU可经由SPD芯片与之进行通讯,从而实现电源管理。低电流电源管理芯片应用于DDR5服务器较小电流的RDIMM内存模组,高电流电源管理芯片则应用于DDR5服务器较大电流的RDIMM和LRDIMM内存模组。 公司可为DDR5系列内存模组提供完整的内存接口及模组配套芯片解决方案,是目前全球可提供全套解决方案的两家公司之一。 3、PCIe Retimer芯片 PCIe Retimer芯片是适用于PCIe高速数据传输协议的超高速时序整合芯片,这是公司在全互连芯片领域布局的一款重要产品。 近年来,高速数据传输协议已由PCIe3.0(数据速率为8GT/S)发展为PCIe4.0(数据速率为16GT/S),再至PCIe5.0(数据速率为32GT/S),数据传输速度翻倍的同时带来了突出的信号衰减和参考时钟时序重整问题,这些问题较大限制了超高速数据传输协议在下一代计算平台的应用范围。PCIe4.0/5.0的高速传输问题提高了对优化高速电路与系统互连的设计需求,加大了在超高速传输下保持信号完整性的研发热度。为了补偿高速信号的损耗,提升信号的质量,通常会在链路中加入超高速时序整合芯片(Retimer)。PCIe Retimer芯片已成为高速电路的重要器件之一,主要解决数据中心数据高速、远距离传输时,信号时序不齐、损耗大、完整性差等问题。 公司的PCIe Retimer芯片,采用先进的信号调理技术来补偿信道损耗并消除各种抖动源的影响,从而提升信号完整性,增加高速信号的有效传输距离,为服务器、存储设备及硬件加速器等应用场景提供可扩展的高性能PCIe互连解决方案。其中,PCIe4.0Retimer芯片符合PCIe4.0基本规范,PCIe5.0/CXL2.0Retimer符合PCIe5.0和CXL2.0基本规范,支持业界主流封装,功耗和传输延时等关键性能指标达到国际先进水平,并已与CPU、PCIe交换芯片、固态硬盘、GPU及网卡等进行了广泛的互操作测试。 2022年,公司PCIe5.0/CXL2.0Retimer芯片完成量产版本的研发,并于2023年1月实现量产。 公司的PCIe4.0/5.0Retimer芯片可应用于AI服务器、NVMe SSD、Riser卡等典型应用场景,同时,公司提供基于该款芯片的参考设计方案、评估板及配套软件等完善的技术支持服务,帮助客户快速完成导入设计,缩短新产品上市周期。 4、MXC芯片 MXC芯片是一款CXL内存扩展控制器芯片,属于CXL协议所定义的第三种设备类型。该芯片支持JEDEC DDR4和DDR5标准,同时也符合CXL2.0规范,支持PCIe5.0的速率。该芯片可为CPU及基于CXL协议的设备提供高带宽、低延迟的高速互连解决方案,从而实现CPU与各CXL设备之间的内存共享,在大幅提升系统性能的同时,显著降低软件堆栈复杂性和数据中心总体拥有成本(TCO)。 该MXC芯片专主要用于内存扩展及内存池化领域,为内存AIC扩展卡、背板及EDSFF内存模组而设计,可大幅扩展内存容量和带宽,满足高性能计算、人工智能等数据密集型应用日益增长的需求,典型应用场景如下: 5、CKD芯片 长久以来,时钟驱动功能集成于寄存时钟驱动器(Register Clock Driver)芯片,在服务器RDIMM或LRDIMM模组上面使用,并未部署到PC端。随着DDR5传输速率持续提升,时钟信号频率越来越高,时钟信号的完整性问题变得日益突出。当DDR5数据速率达到6400MT/s及以上时,PC端内存如台式机及笔记本电脑的UDIMM、SODIMM模组,须采用一颗专用的时钟驱动芯片来对内存模组上的时钟信号进行缓冲再驱动,才能满足高速时钟信号的完整性和可靠性要求。公司已于2022年9月发布业界首款DDR5第一子代时钟驱动器(CKD)工程样片,并已送样给业界主流内存厂商,该产品将用于新一代台式机和笔记本电脑内存。该芯片的主要功能是缓冲来自台式机和笔记本电脑中央处理器的高速内存时钟信号,并将之输出驱动到UDIMM、SODIMM模组上的多个DRAM内存颗粒。该时钟驱动芯片符合JEDEC标准,支持数据速率高达6400MT/s,并支持低功耗管理模式。 津逮服务器平台产品线 津逮服务器平台主要由澜起科技的津逮CPU和混合安全内存模组(HSDIMM)组成。该平台具备芯片级实时安全监控功能,可在信息安全领域发挥重要作用,为云计算数据中心提供更为安全、可靠的运算平台。此外,该平台还融合了先进的异构计算与互联技术,可为大数据及人工智能时代的各种应用提供强大的综合数据处理及计算力支撑。 1、津逮CPU 津逮CPU是公司推出的一系列具有预检测、动态安全监控功能的x86架构处理器,适用于津逮或其他通用的服务器平台。公司先后推出了第一代、第二代、第三代及第四代津逮CPU,以更好满足用户对安全可靠算力日益提升的需求。 2019年5月,公司发布第一代津逮CPU;2020年8月,公司发布第二代津逮CPU;2021年4月,公司发布第三代津逮CPU。2022年10月,公司第三代津逮CPU系列产品通过了VMware公司的产品兼容性认证,达到VMware ESXi7.0U3虚拟化平台的通用兼容性及性能、可靠性要求,满足用户的关键应用需要。 2023年1月12日,公司发布全新第四代津逮CPU,旨在以卓越性能为云计算、企业应用、人工智能及高性能计算提供算力支持。公司第四代津逮CPU以英特尔第四代至强可扩展处理器(代号:Sapphire Rapids)为内核,通过了澜起科技安全预检测(PrC)测试,是面向本土市场的x86架构服务器处理器。相较上一代产品,第四代津逮CPU采用先进的Intel7制程工艺,其最大核心数为48核,最高睿频频率为4.2GHz,最大共享缓存为105MB,关键性能指标大幅提升。同时,在带宽、吞吐、延时等互连性能方面,第四代津逮CPU也实现了一系列重大突破或升级:支持UPI2.0,CPU之间支持4路互连,速率高达16GT/s;内存类型升级为8通道DDR5,速率高达4800MT/s,较DDR4提升50%,单插槽支持16根内存条;支持PCIe5.0,单CPU支持最大80路PCIe通道,传输速率高达32GT/s,较上一代实现翻倍,可支持更高速的网卡、GPGPU卡和存储设备;引入CXL1.1,可支持各类加速卡和内存扩展,在提升系统性能的同时,降低数据中心总体拥有成本。 2、混合安全内存模组(HSDIMM) 混合安全内存模组采用公司具有自主知识产权的Mont-ICMT(Montage,Inspection&Control on Memory Traffic)内存监控技术,可为服务器平台提供更为安全、可靠的内存解决方案。目前,公司推出两大系列混合安全内存模组:标准版混合安全内存模组(HSDIMM)和精简版混合安全内存模组(HSDIMM-Lite),可为不同应用场景提供不同级别的数据安全解决方案,为各大数据中心及云计算服务器等提供了基于内存端的硬件级数据安全解决方案。 津逮服务器平台主要针对中国本土市场,截至目前,已有多家服务器厂商采用津逮服务器平台相关产品,开发出了系列高性能且具有独特安全功能的服务器机型。这些机型已应用到政务、交通等领域及高科技企业中,为用户实现了计算资源池的无缝升级和扩容,在保障强劲运算性能的同时,更为用户的数据、信息安全保驾护航。 AI芯片 1、AI芯片解决方案概述 公司在研的第一代AI芯片解决方案由AI芯片等相关硬件及相应的适配软件构成,采用了近内存计算架构,主要用于解决AI计算在大数据吞吐下推理应用场景中存在的CPU带宽、性能瓶颈及GPU内存容量瓶颈问题,为客户提供低延时、高效率的AI计算解决方案。 AI芯片是上述解决方案的核心硬件,主要由AI计算子系统、CXL控制器、DDR内存控制器等模块组成,其中AI计算子系统具有较强的可扩展性,包含了DSP Cluster和AI Core Cluster,DSP支持通用向量计算,AI Core支持矩阵和张量计算。该芯片面向大数据场景下AI的应用进行了针对性设计,集成了AI高性能计算、异构计算、CXL高速接口技术、DDR内存控制技术等相关技术,具有对大容量数据搜索和排序等高效的硬件加速功能,并且兼具数据压缩和数据加解密等功能。 同时,公司的AI芯片解决方案将支持完善的AI软件生态,能够针对性地对各类AI算法和模型进行软硬件联合深度优化,可支持业内主流的各类神经网络模型,比如视觉算法、自然语言处理和推荐系统等方向,有利于后续软硬件生态建设及市场推广工作。 2、AI芯片未来典型应用场景 公司在研的第一代AI芯片未来的典型应用场景如下: (1)互联网领域大数据吞吐下的推荐系统。目前业界常规方案是将推荐系统中“Embedding(向量化)”、“Embedding Search(向量搜索)”两个主要步骤分别交由不同平台计算平台处理,由高算力的GPU、FPGA或ASIC芯片负责“Embedding”部分,由CPU+大数据系统部署“EmbeddingSearch”部分,这种步骤分割,产生大量的数据交换,并且由于硬件的限制,存在搜索效率的瓶颈。公司AI芯片的目标是整合上述两个步骤,同时平衡算力和内存容量,使计算资源和内存得以高效利用,解决系统的效率瓶颈问题。 (2)NLP(自然语言处理)的应用场景 近期,NLP(自然语言处理模型)的参数量呈现出指数级增加的趋势,对AI芯片的内存容量提出越来越高的要求。针对NLP大模型的相应需求,公司研发的AI芯片在大容量内存和高速互连方面具有业界领先优势。同时具备高稳定性,能高效灵活地支持NLP应用的不断发展。 此外,在医疗领域生物医学/医疗大图片流处理、人工智能物联网领域的大数据应用场景也是公司AI芯片未来的目标市场之一。 总体来说,公司AI芯片解决方案的目标是在类似上述应用场景下,相较于传统方案,可以为客户提供更有效率、更具性价比的解决方案。 3、AI芯片的技术先进性 在第一代AI芯片解决方案的研发过程中,公司自主研发及系统整合了一系列关键的核心技术,攻克了在大数据高性能计算场景下存在的内存墙的技术难点,支持异构多核、高速稳定的互连互通以及与x86软硬件生态的无缝兼容,提升了AI推理计算和大数据吞吐应用场景下的运算效率。其技术先进性主要体现在: (1)AI芯片整体架构采用“基于CXL协议的近内存计算”这一创新的架构,旨在解决数据中心的AI推理计算和大数据融合的业务场景下多方面用户痛点和技术难点; (2)AI计算引擎模块为交互计算的异构计算系统,同时融合高速SRAM及自主研发硬件加速器,并兼备灵活的可编程多核异构设计思路,可同时进行处理命令和数据的高速交互,提高了运算效率; (3)公司的CXL控制器可实现CPU与AI芯片的高速交互,提供了大容量数据搜索和排序等高效的硬件加速功能,并且兼具数据压缩和数据加解密等特色功能; (4)完善的AI软件生态,能够针对性地对各类AI算法和模型进行软硬件联合深度优化,适用于业内主流的各类神经网络模型,并与主流软件框架的完全兼容和无缝对接; (5)自研的灵活可多维扩展的高性能计算核心具备模块设计的理念,有利于AI芯片后续不断迭代升级。 二、核心技术与研发进展 1.核心技术及其先进性以及报告期内的变化情况 (1)核心技术及其先进性 公司具备自有的集成电路设计平台,包括数字信号处理技术、内存管理与数据缓冲技术、模拟电路设计技术、高速逻辑与接口电路设计技术以及低功耗设计技术,方案集成度高,可有效提高系统能效和产品性能。 公司历经十余年的专注研发和持续投入,成为全球可提供从DDR2到DDR5内存全缓冲/半缓冲完整解决方案的主要供应商之一。公司的核心技术完全基于自主知识产权,突破了一系列关键技术壁垒。由公司发明的“1+9”分布式缓冲内存子系统框架,突破了DDR2、DDR3的集中式架构设计,创新性采用1颗寄存缓冲控制器为核心、9颗数据缓冲控制器芯片的分布结构布局,大幅减少了CPU与DRAM颗粒间的负载效应,降低了信号传输损耗,解决了内存子系统大容量与高速度之间的矛盾。该技术架构最终被JEDEC国际标准采纳,提升了国际话语权,为推动国内集成电路设计产业的进步做出了显著的贡献。该架构已在DDR5世代演化为“1+10”框架,继续作为LRDIMM的国际标准。 公司提出了一种内存接口校准算法,发明了新型高速、低抖动收发器,解决了多点通讯、突发模式下内存总线的信号完整性问题。在服务器内存最大负载情况下,该技术可支持DDR4内存实现最高速率(3200MT/s),达到国际领先水平。此外,公司还提出一种先进的内存子系统的低功耗设计技术,发明了新型自适应电源管理电路,并采用动态时钟分配等创新技术,显著降低了相关内存接口芯片产品的功耗。 在DDR5内存接口芯片的研发过程中,公司的核心技术在原有的基础上经过持续不断技术创新与积累,建立了新一代DDR5高速内存接口产品所需的关键设计技术,研发出高速高精度自动化测试技术与测试平台,加快了产品设计、全面评估与迭代速度,为DDR5新一代系列产品的研发奠定了坚实的基础。 在高速接口应用领域,SerDes是一项非常重要的技术,公司正在持续投入研发,该项技术的突破为公司相关新产品的研发奠定了基础。SerDes是SERializer(串行器)/DESerializer(解串器)的简称,它是一种主流的时分多路复用、点对点的串行通信技术,即在发送端将多路低速并行信号转换成高速串行信号,经过传输媒体(光缆或铜缆),最后在接收端将高速串行信号重新转换成低速并行信号。作为一种重要的底层技术,SerDes是相关重要高速传输技术(比如PCIe、USB、以太网等)的物理层基础,广泛应用于服务器、汽车电子、通信等领域的高速互连。 (2)核心技术在报告期内的变化情况 2023年上半年,公司通过在DDR5内存接口芯片技术方面持续投入研发,继续保持在该领域核心技术的领先性,相关技术成果已经在DDR5第三子代内存接口芯片上得以应用。同时,公司在PCIe SerDes IP研发上取得重大进展,相关IP已应用在公司PCIe5.0/CXL2.0Retimer产品中。 2.报告期内获得的研发成果 (1)互连类芯片 Ⅰ、DDR5内存接口芯片 2023年上半年,公司推进DDR5第二子代RCD芯片量产准备工作,并开展DDR5第三子代RCD芯片量产版本的研发。 Ⅱ、MRCD/MDB芯片 2023年上半年,基于客户对DDR5第一子代MRCD/MDB芯片工程样片的反馈意见,公司推进量产版本的研发。 Ⅲ.CKD芯片 2023年上半年,基于客户对DDR5第一子代CKD芯片工程样片的反馈意见及相关标准的更新,公司完成了量产版本的流片及样品制备,目前正在推进量产前的质量认证及客户认证等相关工作。 Ⅳ.PCIe Retimer芯片 2023年1月,公司的PCIe5.0/CXL2.0Retimer芯片实现量产,该芯片符合PCI-SIG和CXL行业组织的相关技术规范,采用业界主流封装,传输速率高达32GT/s,在业界率先支持低于5ns的超低传输时延,同时支持SRIS和Retimer级联等复杂系统拓扑,应对PCIe/CXL信号完整性挑战的理想解决方案。 在完成前述产品量产后,公司已开展PCIe6.0Retimer芯片关键IP的开发及验证工作。 Ⅴ.MXC芯片 2023年上半年,基于客户对第一代MXC芯片工程样片的反馈意见和标准更新,公司完成了量产版本的流片及样品制备,目前正在推进量产前的质量认证及客户认证等相关工作。 ⅤI.时钟发生器芯片 2023年上半年,公司正在推进第一代时钟发生器芯片工程样片的研发工作。 (2)津逮服务器平台 2023年1月,公司正式发布第四代津逮CPU产品,该芯片采用先进的Intel7制程工艺,其最大核心数为48核,最高睿频频率为4.2GHz,最大共享缓存为105MB,关键性能指标大幅提升,在带宽、吞吐、延时等互连性能方面也实现重大突破或升级。 目前正在开展第五代津逮CPU产品研发工作。 (3)AI芯片 2023年上半年,公司开展了第一代AI芯片工程样片的相关测试及验证工作,并在相关应用平台进行业务适配。同时,公司根据AI行业的发展趋势及技术演进,积极推进下一代AI芯片的预研工作。

二、经营情况的讨论与分析

公司是一家国际领先的数据处理及互连芯片设计公司,致力于为云计算和人工智能领域提供高性能、低功耗的芯片解决方案。公司专注于数据处理及互连类芯片两大领域,围绕自身技术优势及市场能力进行产品布局。2023年上半年,受宏观环境影响,服务器及计算机行业需求下滑,面对行业去库存的压力,公司积极应对挑战,第二季度经营情况较第一季度环比改善明显;在产品研发方面,公司稳扎稳打,持续推进产品研发工作并不断拓展公司产品品类,同时把握AIGC带来的行业发展机遇,积极开展相关产品的量产准备工作及市场拓展工作。报告期内具体经营情况如下: 一、积极应对行业去库存挑战,多项经营指标环比改善明显 受服务器及计算机行业需求下滑导致的客户去库存影响,报告期内公司实现营业收入9.28亿元,同比下降51.87%;归属上市公司股东的净利润0.82亿元,同比下降87.98%,剔除股份支付费用影响后的归属于上市公司股东的净利润为1.41亿元,同比下降80.95%,净利润下降的主要原因为:(1)公司营业收入同比下降51.87%;(2)公司保持高强度研发投入,研发投入金额为3.03亿元,同比增长47.03%;(3)公司公允价值变动收益同比减少2.22亿元;(4)公司计提的资产减值损失同比增加1.45亿元。 面对行业去库存的压力,公司迎难而上,积极拓展市场。经过全体员工的努力,公司2023年第二季度多项经营指标环比明显改善。2023年第二季度,随着DDR5内存接口及模组配套芯片出货量较上季度显著提升,公司实现营业收入5.08亿元,环比增长21.11%;实现归属上市公司股东的净利润0.62亿元,环比增长215.08%;剔除股份支付费用影响后的归属于上市公司股东的净利润为0.89亿元,环比增长75.02%;受益于DDR5内存接口芯片出货量占比提升,公司2023年第二季度毛利率为58.83%,较第一季度提升5.54个百分点。 分产品线来看,2023年上半年公司互连类芯片产品线实现销售收入9.10亿元,同比下降26.37%,毛利率为57.01%,其中第二季度该产品线实现销售收入4.98亿元,环比增长20.57%,毛利率为59.55%,较第一季度提升5.6个百分点;津逮服务器平台产品线实现销售收入0.14亿元,同比下降98.00%,毛利率为15.37%。 截至2023年6月30日,公司总资产109.43亿元,较年初增长2.41%;归属于母公司的所有者权益101.15亿元,较年初增长2.04%。 二、持续加大研发投入拓宽产品品类,稳步开展产品研发工作 2023年上半年,公司持续加大研发投入,报告期内公司研发费用为3.03亿元,同比增长47.03%,研发费用占营业收入的比例为32.63%。随着持续的研发投入以及核心技术的积累,公司不断拓宽产品品类,报告期内公司稳步推进产品的研发及迭代升级。 1、已量产产品 报告期内,公司量产了PCIe5.0/CXL2.0Retimer芯片及第四代津逮CPU产品。 2、研发阶段产品 报告期内,在互连类芯片领域,公司正按计划稳步推进DDR5第二/第三子代RCD芯片、DDR5第一子代MRCD/MDB芯片、DDR5第一子代CKD芯片、第一代MXC芯片等产品量产版本的研发,以及时钟发生器等产品的工程研发;在AI芯片领域,公司进行了第一代AI芯片工程样片的相关测试及验证,并在相关应用平台业务适配。 3、研发人员及知识产权 作为一家以人才为核心的集成电路设计企业,公司广纳优秀研发技术人才,研发技术团队规模持续扩大。截至2023年上半年末,公司研发技术人员为515人,较2022年底净增加47人,占公司总人数的比例为75%,其中硕士及以上学历的占研发技术人员总数的64%。 在知识产权方面,2023年上半年,公司共获得7项授权发明专利,新申请了21项发明专利;新申请并获得1项集成电路布图设计;新获得2项软件著作权登记。 三、把握AIGC带来的行业发展机遇,推进相关产品量产工作 根据相关行业分析,AIGC的快速发展将推动AI服务器增长,从而拉动相关芯片的需求。对公司相关产品的影响主要体现在以下四个方面: 1、AI应用将增加对内存容量和带宽的需求,相应带动服务器内存接口及配套芯片的需求保持稳定向上,并进一步增加对DDR5高带宽内存模组(MRDIMM)的需求。据行业分析认为,未来随着支持MRDIMM的CPU平台上市,MRDIMM的渗透率将有望得到明显提升,MRCD/DB芯片作为MRDIMM的标准配置,其需求量将随之而增长。与用于RDIMM的RCD/DB芯片相比,用于MRDIMM的MRCD/MDB芯片设计更为复杂、支持速率更高,意味着它的价值量较普通的RCD/DB芯片将有所提升。更重要的是,由于MRDIMM采用了“1颗MRCD+10颗MDB”的架构,将极大增加行业对MDB芯片的需求。公司是DDR5MDB芯片国际标准的牵头制定者,相关技术处于国际领先水平。报告期内,公司积极推进DDR5MRCD/MDB芯片的研发,并计划在年底前完成相关研发工作并推动第一子代产品量产,待量产后,有望在该产品未来的全球市场中占据重要份额。 2、随着对内存容量需求的不断增长,未来对内存扩展和内存池化的应用需求将随之增长,这将为CXL内存扩展控制器芯片(MXC)带来长期广阔的成长空间。美光科技与投资者交流时曾预测CXL相关产品的市场规模,到2025年预计将达到20亿美金,到2030年有望超过200亿美金。MXC是CXL内存扩展和内存池化相关应用的核心控制芯片,行业预期MXC芯片将在上述市场规模中占据重要价值。公司于2022年5月全球首发MXC芯片,相关技术引领全球。报告期内,公司完成了第一代MXC芯片量产版本的流片及样品制备,目前正在推进量产前的相关准备工作,有望在未来的全球市场竞争中抢得先机。今年5月,三星电子推出其首款支持CXL2.0的128GB DRAM,并表示将于今年量产,加速下一代存储器解决方案的商用化,澜起的MXC芯片被用于该解决方案,是其中的核心控制芯片。 3、随着AI应用的增长,需要配置GPU BOX的场景越来越多,将增加对PCIe Retimer芯片的需求。以一台典型的配8个GPU的AI服务器为例,考虑到对信号稳定性和传输速率的要求,大概率需要配置8颗PCIe Retimer芯片,部分型号可能需要配置16颗PCIe Retimer芯片。公司是全球可提供PCIe4.0Retimer芯片的三家主要厂商之一,同时,公司在报告期内成功量产PCIe5.0/CXL2.0Retimer芯片,是全球第二家量产该产品的厂家。针对AI服务器等典型应用场景,公司可提供基于PCIe5.0/CXL2.0Retimer芯片的参考设计方案、评估板及配套软件等完善的技术支持服务,帮助客户快速完成导入设计,缩短新产品上市周期。报告期内公司积极开展PCIe Retimer芯片的客户导入及相关市场拓展工作,有望直接受益于该产品市场规模的增长。 4、AI应用将带动对算力需求的持续增长,公司在研的AI芯片正是针对大数据吞吐下的AI推理应用,有望持续受益于相关AI细分行业快速发展的影响。 此外,随着DDR5相关技术的快速发展,以及支持速率的不断提高,PC端内存模组将产生新的芯片需求。根据全球行业标准组织JEDEC的定义,当DDR5数据速率达到6400MT/s及以上时,PC端的内存模组(台式机的UDIMM及笔记本电脑的SODIMM)须采用一颗专用的CKD芯片,对内存模组上的时钟信号进行缓冲再驱动,以满足高速时钟信号的完整性和可靠性要求。CKD芯片对于行业来说将是全新的市场增量,届时CKD每年的需求量将与当年所需的DDR5UDIMM和SODIMM数量(支持速率为6400MT/s及以上)呈正相关。继去年5月公司发布业界首款DDR5CKD芯片工程样片后,报告期内,公司完成了量产版本的流片及样品制备,目前正在推进量产前的准备工作,待量产后,有望在该产品未来的全球市场中占据重要份额。 四、聚焦细节持续改进ESG相关工作,提升公司ESG管理水平 2023年上半年,公司发布了《2022年度环境、社会及公司治理报告》,首次系统的披露了公司相关的碳排放数据。为提升整体的ESG管理水平,公司进一步完善ESG管治架构体系,同时,系统性梳理公司各部门ESG工作现状,识别ESG提升方向,在完善制度、夯实数据基础等领域开展针对性改善提升,以实现公司与利益相关方的价值共创、共享与共荣。三、风险因素

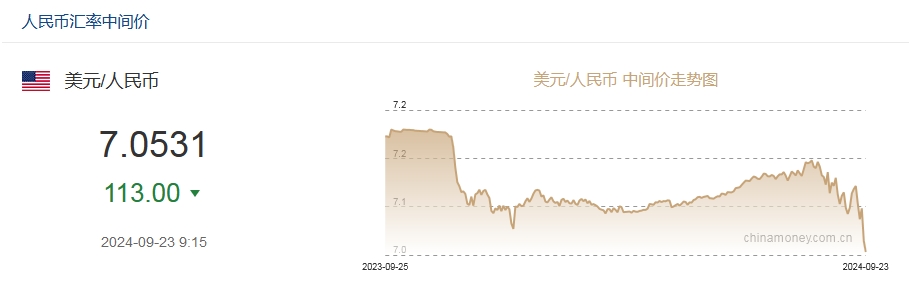

(一)核心竞争力风险 1、产品研发风险 集成电路产业发展日新月异,技术及产品迭代速度较快。芯片设计公司需要不断地进行创新,同时对市场进行精确的把握与判断,不断推出适应市场需求的新技术、新产品以跟上市场变化,赢得和巩固公司的竞争优势和市场地位。 公司新产品的开发风险主要来自以下几个方面:(1)公司新产品的开发存在周期较长、资金投入较大的特点,在产品规划阶段,存在对市场需求判断失误的风险,可能导致公司产品定位错误;(2)由于公司产品技术含量较高,公司存在对企业自身实力判断失误的风险,主要是对公司技术开发能力的判断错误,导致公司研发项目无法实现或周期延长;(3)由于先发性对于公司产品占据市场份额起到较大的作用,若产品迭代期间,竞争对手优先于公司设计生产出新一代产品,公司有可能丢失较大的市场份额,从而影响公司后续的发展。 针对上述潜在风险,一方面,公司将加强对行业新技术、新需求的动态跟踪,加强对市场需求的研判能力;另一方面,公司积极参与各类行业标准组织,参与甚至主导相关新产品标准的制定,从而降低后续产品研发风险。 2、人才流失风险 芯片设计行业属于技术密集型产业,对技术人员的依赖度较高。凭借公司研发团队多年来的持续努力钻研,公司技术人员的自主开发能力不断增强。公司针对优秀人才实施了多项激励措施,对稳定公司核心技术团队起到了积极作用。但同行业竞争对手仍可能通过更优厚的待遇吸引公司技术人才,或公司受其他因素影响导致公司技术人才流失,将对公司新产品的研发以及技术能力的储备造成影响,进而对公司的盈利能力产生一定的不利影响。 针对上述潜在风险,一方面,公司为员工提供丰富的职业发展机会,让员工在企业中获得成长;另一方面,伴随着企业的发展壮大,合理提升员工待遇,实施股权激励在内的多种激励手段,从而吸引和留住优秀人才。 3、技术泄密风险 通过持续技术创新,公司研发技术平台处于行业内较高水平。自成立以来,公司就十分重视对核心技术的保密,及时将研发成果申请专利,并制定了严格完善的内控制度,保障核心技术的保密性。但存在由于核心技术人员流动、技术泄密,或专利保护措施不力等原因,导致公司核心技术流失的风险。如前述情况发生,将在一定程度上削弱公司的技术优势,对公司的竞争力产生不利影响。 (二)经营风险 1、客户集中风险 互连类芯片产品线是公司目前主要的利润来源,其中内存接口芯片产品的下游为DRAM市场,直接客户为内存模组厂商。根据相关行业统计数据,在DRAM市场三星电子、海力士、美光科技位居行业前三名,市场占有率合计超过90%,这导致公司在该产品线的客户集中度也相对较高。如果公司产品开发策略不符合市场变化或不符合客户需求,则公司将存在不能持续、稳定地开拓新客户和维系老客户新增业务的可能,从而面临业绩下滑的风险。同时,由于客户相对集中度高,如果发生客户要求大规模降价、竞争对手恶性竞争等竞争环境变化的情形,公司将面临市场份额波动、收入下滑的风险。 公司正积极研发和推广新产品,通过扩大产品种类,降低单一产品的客户集中风险。 2、供应商风险 公司为最大程度优化自身产能资源配置,同时考虑经济性原则,采取Fabless模式,将芯片生产及封测等工序交给外协厂商负责。自公司成立以来,公司已与外协加工厂商建立了稳定、良好的协作关系,外协加工厂商严格按照公司的设计图纸及具体要求进行部分工序的作业。采用外协加工的模式有利于公司将资源投入到核心工序、核心技术研究和产品研发中去,以增强核心竞争力。但是公司存在因外协工厂生产排期导致供应量不足、供应延期或外协工厂生产工艺存在不符合公司要求的潜在风险。 此外,晶圆制造、封装测试均为资本及技术密集型产业,因此相关行业集中度较高,是行业普遍现象。公司供应商集中度较高。如果上述供应商发生不可抗力的突发事件,或因集成电路市场需求旺盛出现产能紧张等因素,晶圆代工和封装测试产能可能无法满足公司需求,将对公司经营业绩产生一定的不利影响。如果市场环境及供求关系发生变化,造成原材料价格上涨等情形,公司将面临成本上升、毛利率下降等相关经营风险。 3、津逮服务器平台业务波动的风险 服务器市场既是未来数据中心市场的重要组成部分,也是公司未来布局云计算、大数据、人工智能等新兴领域的重要抓手。津逮服务器平台技术壁垒高,市场门槛高,客户验证周期长,经过前期的市场推广和客户培育,报告期内公司的津逮CPU稳步发展,目前津逮CPU已经广泛应用于金融、政务、交通、数据中心等领域。但津逮CPU业务在其发展初期需求并不稳定,不排除因市场、政策、客户、产能等因素的影响而导致相关业务存在短期波动或不及预期,2023年上半年,受宏观环境及行业去库存等因素影响,津逮服务器平台产品线需求下降,后续如果上述影响未能消除,可能会对公司未来营业收入造成一定的扰动。 4、产品质量风险 公司采用Fabless的运营模式,专注于芯片的设计及研发环节,而芯片的生产制造、封装测试则通过委外方式完成。公司的产品质量一方面取决于公司的研发设计水平,一方面取决于委外厂商的生产管理水平。如果公司产品设计出现缺陷,或委外厂商生产管理水平不足导致发生产品质量事故,将给公司造成直接经济损失,存在赔偿客户以及造成公司订单减少、收入下滑、盈利下降等风险。 5、存货跌价风险 公司存货主要由原材料、委托加工物资、库存商品构成。2023年上半年,公司综合考虑库龄及市场价格等因素,对截至2023年6月30日的存货(主要为津逮CPU)进行了资产减值测试,计提存货跌价准备1.45亿元,计提后公司的存货账面价值为7.36亿元。若未来市场环境发生变化、竞争加剧或技术更新导致存货过时,使得产品滞销、存货积压,将导致公司存货跌价风险进一步增加,对公司的盈利能力产生不利影响。 6、知识产权风险 芯片设计属于技术密集型行业,该行业知识产权众多。在产品开发过程中,涉及到较多专利及集成电路布图等知识产权的授权与许可,因此公司出于长期发展的战略考虑,一直坚持自主创新的研发战略,做好自身的知识产权的申报和保护,并在需要时购买必须的第三方知识产权,避免侵犯他人知识产权。但未来不能排除竞争对手或第三方采取恶意诉讼的策略,阻滞公司市场拓展的可能性。同时,也不能排除竞争对手窃取公司知识产权非法获利的可能性。 (三)财务风险 汇兑损益风险 公司日常经营的销售采购业务大部分以美元结算,且发生的外币交易在初始确认时,按交易日的上一月的期末汇率折算为记账本位币金额,但在资产负债表日,对于外币货币性项目采用资产负债表日即期汇率折算为记账本位币金额,导致公司汇兑损益金额较大。 2023年上半年,公司外汇汇兑收益为人民币98.77万元。由于人民币对美元汇率的持续波动,公司存在汇兑损失的风险。 在所有其他变量保持不变的假设下,人民币兑美元汇率发生合理、可能的变动时, (四)行业风险 公司是集成电路设计企业,主要从事集成电路芯片产品的设计、研发及销售,属于集成电路行业的上游环节。集成电路行业是资本及技术密集型行业,随着技术的更迭,行业本身呈现周期性波动的特点,并且行业周期的波动与经济周期关系紧密。受宏观环境影响,2023年服务器及计算机行业需求下滑,相关芯片处于去库存阶段,公司亦面临下游客户去库存的压力,可能对公司全年经营业绩造成不利影响。 (五)宏观环境风险 1、全球贸易摩擦风险 报告期内,公司的主要客户、供应商、EDA工具授权厂商大多为境外企业。近年来,全球贸易摩擦频发,虽然目前未对公司的经营情况产生重大不利影响,但鉴于集成电路产业是典型的全球化分工合作行业,如果全球贸易摩擦进一步升级,有可能造成产业链上下游交易成本增加,下游需求受限,上游供给不畅,从而将对公司的经营造成不利影响。 2022年以来,美国出台一系列半导体出口管制政策,根据在此领域的专业美国律师事务所的分析,截至目前相关规则对公司业务及相关人员均无直接影响。如果相关半导体出口管制政策持续加码,不排除未来对公司业务及相关人员产生不利影响。公司将持续关注相关规则的更新并积极做好应对措施。 2、税收优惠政策风险 根据《财政部税务总局发展改革委工业和信息化部关于促进集成电路产业和软件产业高质量发展企业所得税政策的公告》(财政部税务总局发展改革委工业和信息化部公告2020年第45号)及《国家发展改革委等部门关于做好2023年享受税收优惠政策的集成电路企业或项目、软件企业清单制定工作有关要求的通知》(发改高技〔2023〕287号),母公司符合国家鼓励的重点集成电路设计企业的认定标准,减按10%的适用税率缴纳企业所得税。 根据《财政部税务总局发展改革委工业和信息化部关于促进集成电路产业和软件产业高质量发展企业所得税政策的公告》(财政部税务总局发展改革委工业和信息化部公告2020年第45号)及《国家鼓励的集成电路设计、装备、材料、封装、测试企业条件公告》(工业和信息化部公告2021年第9号)的规定,国家鼓励的集成电路设计企业,可自获利年度起第一年至第二年免征企业所得税,第三年至第五年按照25%的法定税率减半征收企业所得税,澜起电子科技(昆山)有限公司(以下简称“澜起昆山”)符合国家鼓励的集成电路设计企业的认定标准,可自2022年度起享受上述税收优惠,2022年度免征企业所得税。 若未来上述税收优惠政策发生调整,或者公司不再满足享受以上税收优惠政策的条件,则将对公司的经营业绩产生一定影响。 假设澜起昆山不再符合国家鼓励的集成电路设计企业的认定标准,但仍属于高新技术企业,将适用15%的企业所得税税率,则2023上半年将增加872.79万元所得税费用,减少872.79万元净利润;假设澜起昆山不再符合国家鼓励的集成电路设计企业的认定标准,且不属于高新技术企业,将适用25%的企业所得税税率,则2023年上半年将增加1,104.99万元所得税费用,减少1,104.99万元净利润。四、报告期内核心竞争力分析

(一)核心竞争力分析 1、持续的创新研发能力与领先的技术优势 公司自创立以来,持续专注于技术研发和产品创新。公司具备自有的集成电路设计平台,包括数字信号处理技术、内存管理与数据缓冲技术、模拟电路设计技术、高速逻辑与接口电路设计技术以及低功耗设计技术,方案集成度高,可有效提高系统能效和产品性能。 在内存接口技术领域,公司以技术创新为基础,发明了DDR4全缓冲“1+9”架构,最终被JEDEC国际标准采纳,该架构在DDR5世代演化为“1+10”框架,继续作为LRDIMM的国际标准。在DDR5世代,公司牵头制定DDR5第一子代、第二子代、第三子代内存接口芯片国际标准,巩固了公司在该领域的技术领先地位。澜起科技凭借具有自主知识产权的高速、低功耗技术,为新一代服务器平台提供完全符合JEDEC标准的高性能内存接口解决方案,是全球可提供从DDR2到DDR5内存全缓冲/半缓冲完整解决方案的主要供应商之一,在该领域拥有重要话语权。经过持续不断的技术创新与积累,公司的核心技术在DDR4系列产品原有的基础上,建立了新一代DDR5高速内存接口产品所需的关键设计技术,研发出高速高精度自动化测试技术与测试平台。2022年,公司在业界率先试产DDR5第二子代RCD芯片,并在业界率先推出DDR5第三子代RCD芯片工程样片、DDR5第一子代CKD芯片工程样片,再次体现了公司在内存接口技术领域的全球领先地位。DDR5世代,公司继续领跑,内存接口芯片的市场份额保持稳定,同时,公司可为DDR5系列内存模组提供完整的内存接口及模组配套芯片解决方案,是目前全球可提供全套解决方案的两家厂商之一。 在PCIe技术领域,公司是全球能够提供PCIe4.0Retimer芯片的三家厂商之一,是全球第二家宣布量产PCIe5.0/CXL2.0Retimer芯片的厂家。作为PCIe相关的底层技术,公司的Serdes IP已实现突破,相关IP已应用到公司PCIe5.0/CXL2.0Retimer芯片上。 在CXL技术领域,公司提前进行战略布局,并于2022年5月发布全球首款CXL内存扩展控制器芯片(MXC),相关技术处于国际领先水平。MXC芯片专为内存AIC扩展卡、背板及EDSFF内存模组而设计,可大幅扩展内存容量和带宽,满足高性能计算、人工智能等数据密集型应用日益增长的需求。MXC芯片推出以来,公司迅速和国内外主要的模组厂商,服务器系统厂商和云服务厂商展开合作,积极推进基于MXC芯片的模组项目设计。目前已经有多家客户推出了采用澜起科技MXC芯片的CXL内存模组及板卡,并在相关服务器平台上通过基本功能验证。公司也在进一步与更多合作伙伴一起探索CXL内存扩展和池化在实际业务场景中的应用和落地,保持在这一市场中的领先优势。 公司的核心技术基于自主知识产权,并形成了有规划、有策略的专利布局。截至报告期末,公司已获授权的国内外发明专利达151项。 2、领先的市场地位和品牌优势 经过19年的发展和积淀,公司已成为国际知名的芯片设计公司,目前公司核心产品内存接口芯片广泛应用于各类服务器,终端客户涵盖众多知名的国内外互联网企业及服务器厂商,在全球内存接口芯片领域的竞争中处于领先地位,实现国内自主研发产品在该领域的突破。公司成立至今获得了多项荣誉,形成了独特的品牌优势。2016年6月,中国电子学会认定公司“低功耗DDR系列内存缓冲控制器芯片设计技术整体技术达到国际领先水平”;同年12月,该项技术及产业化项目荣获“中国电子学会科学技术奖一等奖”;2017年,公司荣获三星电子颁发的“最佳供应商奖”;2018年,公司产品“第二代DDR4内存缓冲控制器芯片”荣获“‘中国芯’年度重大创新突破产品”奖;2018年11月,津逮服务器CPU及其平台采用的“动态安全监控技术”获评第五届世界互联网大会“世界互联网领先科技成果”;2019年5月,公司“高性能DDR内存缓冲控制器芯片设计技术项目”荣获上海市人民政府颁发的“上海市技术发明一等奖”;2020年10月,公司荣获“上海知识产权创新奖”,公司的津逮CPU荣获“中国芯年度重大创新突破产品奖”;2021年4月,公司PCIe4.0Retimer芯片荣获第九届“中国电子信息博览会创新奖”,同年,公司当选为工信部“制造业单项冠军示范企业”。2022年4月,公司荣获“第二十三届中国专利优秀奖”。2022年11月,公司获得全球领先的内存和存储厂商美光科技的肯定,荣膺美光科技“杰出性能奖(半导体元器件)”和“杰出质量奖(封装&测试材料半导体元器件)”。2023年1月,公司荣获“国家知识产权优势企业”。这一系列荣誉的获得,充分显示出市场对于公司品牌的认可。 3、全球化的产业布局 公司不仅扎根中国,还在美国、韩国等地建立了分支机构或办事处,派驻工程师及销售人员直接对接众多国际产业巨头,深入了解行业发展及技术水平变化趋势,亲身经历整个行业变更,把握瞬息万变的行业动态及创新方向,有效地提升了公司的国际市场影响力及研发效率。同时通过全球化的产业布局,公司可以合理调配全产业资源,发挥产业协同效应,提高了公司的运营效率,有效地控制了成本。 4、人才优势 公司董事长兼首席执行官杨崇和博士曾在美国国家半导体公司等企业任职,并于1997年与同仁共同创建硅谷模式的集成电路设计公司新涛科技。杨崇和博士于2010年当选美国电气和电子工程师协会院士(IEEE Fellow),积累了丰富的设计、研发和管理经验,于2015年入选全球半导体联盟亚太领袖。杨博士在2019年成为全球微电子行业标准制定机构JEDEC“杰出管理领袖奖”首位获奖者,该奖为JEDEC组织新设立奖项,用于表彰推动和支持JEDEC标准发展的电子行业最杰出的高级管理人士。2022年11月,杨博士被授予IEEE终身院士(IEEE Life Fellow)称号,以表彰他多年来在集成电路设计领域做出的杰出贡献。公司总经理Stephen Kuong-Io Tai先生曾参与创建Marvell科技集团并就任该公司的工程研发总监,拥有逾25年的半导体架构、设计和工程管理经验。公司核心技术人员、研发部负责人常仲元博士曾在IEEE学术期刊和国际会议上发表了论文逾20篇,其中3篇发表于ISSCC会议,并作为第一作者出版了《Low Noise Wideband Amplifiers in Bipolar and CMOS Technology》。公司在JEDEC组织中的三个委员会及分会中安排员工担任主席职位,成为细分领域国际行业标准制定的深入参与者。公司入选全球微电子行业标准制定机构JEDEC固态技术协会董事会,是三家入选JEDEC董事会的中国企业之一。 公司核心团队多毕业于国内外著名高校,在技术研发、市场销售、工程管理等领域均有着丰富的阅历和实战经验。公司自成立以来就十分注重人才的培养和创新,目前已培养了数百名在高速、低功耗和数模混合电路设计领域的专业技术人才。目前公司员工中约75%为研发技术人员,且研发技术人员中约64%拥有硕士及以上学位,为公司持续的产品创新提供了重要的人才基础。 5、显著的行业生态优势 公司深耕于服务器内存接口芯片市场,与全球主流的处理器供应商、服务器厂商、内存模组厂商及软件系统提供商,建立了长期稳定的合作关系。自2016年,公司携手英特尔、清华大学及国内知名服务器厂商,进一步开发津逮服务器平台产品,大力拓展数据中心产品市场。公司在芯片设计技术上长期积累,并深度参与行业标准制定。通过与行业生态系统内主要企业的协同、分工、合作,公司深度优化整合行业生态系统内市场资源和技术资源,具备显著的行业生态优势。